Ein Turbo für die künstliche Intelligenz

Sparsame Chips nach dem Vorbild der Natur

Computer verbrauchen große Energiemengen, weil Speicherung und Berechnung der Daten in getrennten Bauteilen stattfinden. Forscher aus Jülich wollen nun sparsame Chips nach dem Vorbild der Natur entwickeln. Die Technologie bietet viele Chancen, speziell für KI-Anwendungen. In der Region soll ein international sichtbarer Forschungs- und Entwicklungsstandort geschaffen werden, um den Transfer in die Industrie zu beschleunigen und den Strukturwandel im Rheinischen Revier zu unterstützen.

In den vergangenen Jahrzehnten sind Computerchips immer leistungsfähiger geworden, die Schaltkreise immer kleiner. Der Energieverbrauch hingegen ist kontinuierlich gestiegen. Denn trotz allem Fortschritt hat sich der grundlegende Aufbau der Rechenmaschinen von Anfang an niemals verändert. Die allermeisten Computer beruhen heute auf der Von-Neumann-Architektur: Das Herz ist der Prozessor. Er führt alle Berechnungen aus. Die dazu nötigen Daten befinden sich aber in einem räumlich getrennten Arbeitsspeicher. Der Austausch von Daten zwischen den beiden Komponenten lässt die Schaltkreise heiß laufen.

Dabei existieren Konzepte für alternative Architekturen, erklärt Stephan Menzel: „Das nennt sich Computation-in-Memory. Dabei werden die Berechnungen direkt im Speicher durchgeführt. So spart man sich die Kommunikation zwischen dem Speicher und dem Prozessor. Und das wiederum senkt den Energieverbrauch des Rechners deutlich.“ Für spezielle Anwendungen kann der Energiebedarf sogar bis auf rund ein Tausendstel zusammenschrumpfen.

Gemeinsam mit seinen Kolleginnen und Kollegen am Jülicher Peter Grünberg Institut (PGI-7) und an der RWTH Aachen forscht er im Rahmen der JARA-Kooperation an solchen sparsamen Bauteilen. Diese basieren nicht auf herkömmlichen Transistoren, sondern auf sogenannten Memristoren (Memory=Speicher + Resistor=Widerstand). Deren Schalteigenschaften weisen ähnliche Charakteristika auf wie die Synapsen im menschlichen Gehirn.

Für seine neuartigen Schaltkreise hat Stephan Menzel eine besonders energie- und rechenintensive Anwendung im Blick: künstliche Intelligenz (KI), speziell: künstliche neuronale Netzwerke. „Diese Algorithmen können verborgene Muster erkennen. Sie identifizieren zum Beispiel Gesichter, verbessern die Wettervorhersage oder unterstützen Ärzte bei ihrer Diagnose“, sagt Stephan Menzel. Diese KI-Systeme lernen, die relevanten Informationen aus einem Datenberg herauszufiltern.

Dazu müssen sie zunächst mit einer großen Menge an Trainingsdaten gefüttert werden. Sollen die Algorithmen beispielsweise auf Fotos menschliche Gesichter erkennen, so müssen sie zunächst einmal anhand unzähliger Portraits lernen, was ein menschliches Gesicht ausmacht. Die Berechnungen dahinter sind so umfangreich, dass diese Programme üblicherweise auf Hochleistungsrechnern laufen. Deren Architektur ist an diese Aufgabe zwar besser angepasst als konventionelle Prozessoren. Doch die Parallelverarbeitung der Daten verschlingt noch immer eine große Menge Energie.

Mit einem speziellen Bauteil wollen Stephan Menzel und sein Kollege Tobias Ziegler in JARA-FIT den KI-Rechnen auf die Sprünge helfen und sie gleichzeitig sparsamer machen. „Wir haben – zunächst noch im kleinen Maßstab – einen Hardware-Beschleuniger verwirklicht, der das Potential hat, künstliche neuronale Netzwerke schneller und effizienter berechnen zu können“, erläutert Tobias Ziegler.

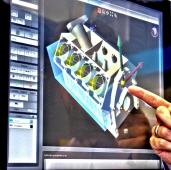

Künstliche neuronale Netzwerke stecken mittlerweile hinter einem Großteil von KI-Systemen. Ihre Arbeitsweise orientiert sich an der Datenverarbeitung im Gehirn. Im menschlichen Denkapparat tauschen die einzelnen Nervenzellen über tausende von Synapsen ihre Impulse aus. Beim Lernen verstärken oder schwächen sich gezielt diese Kontaktstellen. Im künstlichen Gegenstück rechnen dagegen „mathematische Neuronen“, die ebenfalls mit anderen Zellen in Verbindung stehen. Die Stärke dieser Verbindung, Gewicht genannt, verändert sich ebenfalls beim Lernen der Trainingsdaten.

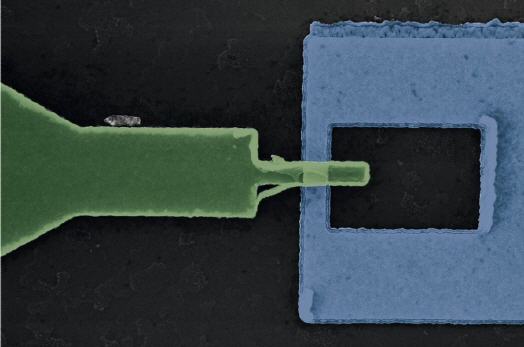

In einem herkömmlichen Rechner müssen dazu viele Daten zwischen Prozessor und Speicher hin und her geschaufelt werden. Die „neuromorphen“ Schaltungen, die Stephan Menzel und seine Kollegen entwickeln, können neuronale Netze mit ihren Synapsen dagegen direkt nachbilden. Gerechnet wird dann direkt im Speicher. Möglich machen dies winzige Widerstandsschalter, aus denen die Schaltungen bestehen.

Stephan Menzel: „Mit diesen Bauelementen, Memristoren, beschäftigen wir uns hier am Institut bereits seit vielen Jahren. Ihr elektrischer Widerstand lässt sich zwischen zwei Zuständen hin und her schalten – zwischen einem hohen und einem niedrigen Wert.“

Der jeweilige Wert bleibt auch dann noch bestehen, wenn die Schaltspannung nicht mehr anliegt. Die Schalter eignen sich daher als nichtflüchtiger Speicher für Daten. Aber sie können noch mehr. Kombiniert man mehrere dieser Schalter, lassen sich damit lange Zeilen aus Speicherzellen aufbauen, die über eine gemeinsame Elektrode miteinander in Kontakt stehen. In dieser Anordnung lassen sich Rechenoperationen direkt an Ort und Stelle auf gespeicherte Informationen anwenden.

Im NEUROTEC-Projekt erprobt die Forschungsgruppe am PGI-7 das Konzept nun erstmals in der Praxis, um mit den Schaltern Berechnungen für die KI durchzuführen. „Wir speicherten zunächst einige Gewichte in dieser Anordnung, sozusagen einen Teil des Trainingsergebnisses. Dann haben wir die zu berechnenden Daten in Spannungssignale kodiert und die Spannungsänderung an der gemeinsamen Elektrode gemessen“, erläutert Tobias Ziegler.

Die Jülicher Forscher sind nicht als einzige an dem Thema dran. Mittlerweile beschäftigen sich Firmen und Forschungsgruppen auf der ganzen Welt mit der Entwicklung von neuromorphen Schaltungen, die auf Memristoren basieren. Das von Tobias Ziegler und seinen Kollegen verfolgte Schaltungskonzept weist gegenüber dem Standard-Design aber eine Besonderheit auf: Die memristiven Bauelemente werden nicht einzeln angesteuert. Die Zellen werden stattdessen immer paarweise komplementär verschaltet.

„Die Zellen werden immer genau entgegengesetzt, betrieben. Wenn die eine einen niedrigen Widerstand hat, dann erhält ihr Gegenstück einen hohen. Unterm Strich hat man also immer einen niedrigen und einen hohen Widerstandswert“, erklärt Stephan Menzel.

Diese alternative Anordnung birgt für die Praxis einen möglicherweise entscheidenden Vorteil. Denn die Spannung steigt so linear, wenn sich der ausgelesene Wert erhöht.

„Ich denke, dass der lineare Spannungsausgang deutlich zur Vereinfachung der Peripherie beiträgt“, erklärt Stephan Menzel. „Ein linearer Spannungsanstieg ist deutlich einfacher zu handhaben. Praktisch jede Ausleseelektronik ist darauf ausgelegt.“ Dass man diesen Teil der Elektronik nicht vernachlässigen sollte, zeigt noch eine andere Zahl: „In Computation-In-Memory-Ansätzen, die andere Gruppen untersucht haben, entfallen mehr als 95 Prozent der Fläche und mehr als 90 Prozent der Leistung auf die Auswahl- und Ausleseelektronik“, ergänzt Tobias Ziegler.

Eine erste Schaltung mit 14 Zellen haben die Jülicher Forscher bereits verwirklicht. Die Machbarkeit ihres Konzepts konnten sie damit unter Beweis stellen. Im nächsten Schritt soll nun ein Demonstrator klären, wie sich das Konzept in der Praxis schlägt. Im Frühjahr 2021 soll ein erster Test-Chip fertig werden, der noch memristive Bauelemente eines kommerziellen Herstellers enthält.

Im weiteren Verlauf des Neurotec-Projekts wollen die Memristor-Spezialisten aus Jülich dann auch Chips mit eigenen memristiven Bauelementen auf den Prüfstand stellen. In einem Performancevergleich wird sich dann zeigen, wie verschiedene Schaltungsentwürfe und Materialen in der Praxis abschneiden.

Man darf gespannt sein, welches Konzept sich am Ende durchsetzt, für diese neuromorphen Chips, die Speicher und Prozessor vereinen. Denn darin sehen viele Fachleute den Schlüssel für energiesparende und schnelle KI-Hardware der Zukunft.

Mehr Informationen zum Forschungszentrum Jülich:

|

Forschungszentrum Jülich GmbH |

|

Wilhelm-Johnen-Straße |

|

52428 Jülich |

|

Tel.: 02461 61-0 |

|

Fax: 02461 61-8100 |

|

E-Mail: info@fz-juelich.de |

|

www.fz-juelich.de |

War dieser Artikel für Sie hilfreich?

|

|

|

|

|

Bitte bewerten Sie diese Seite durch Klick auf die Symbole.

Zugriffe heute: 2 - gesamt: 5800.